# **2020 Research Day**

**Spin-Transfer Torque MTJs in Logic and Cache Memory Applications**

Esteban Garzón<sup>1, 2</sup>, Raffaele De Rose<sup>1</sup>, Felice Crupi<sup>1</sup>, Marco Lanuzza<sup>1</sup>, Adam Teman<sup>2</sup>

<sup>1</sup>DIMES, University of Calabria, Rende 87036, Italy | <sup>2</sup>EnICS Laboratory, Bar-Ilan University, Ramat Gan 5290002, Israel

# Introduction

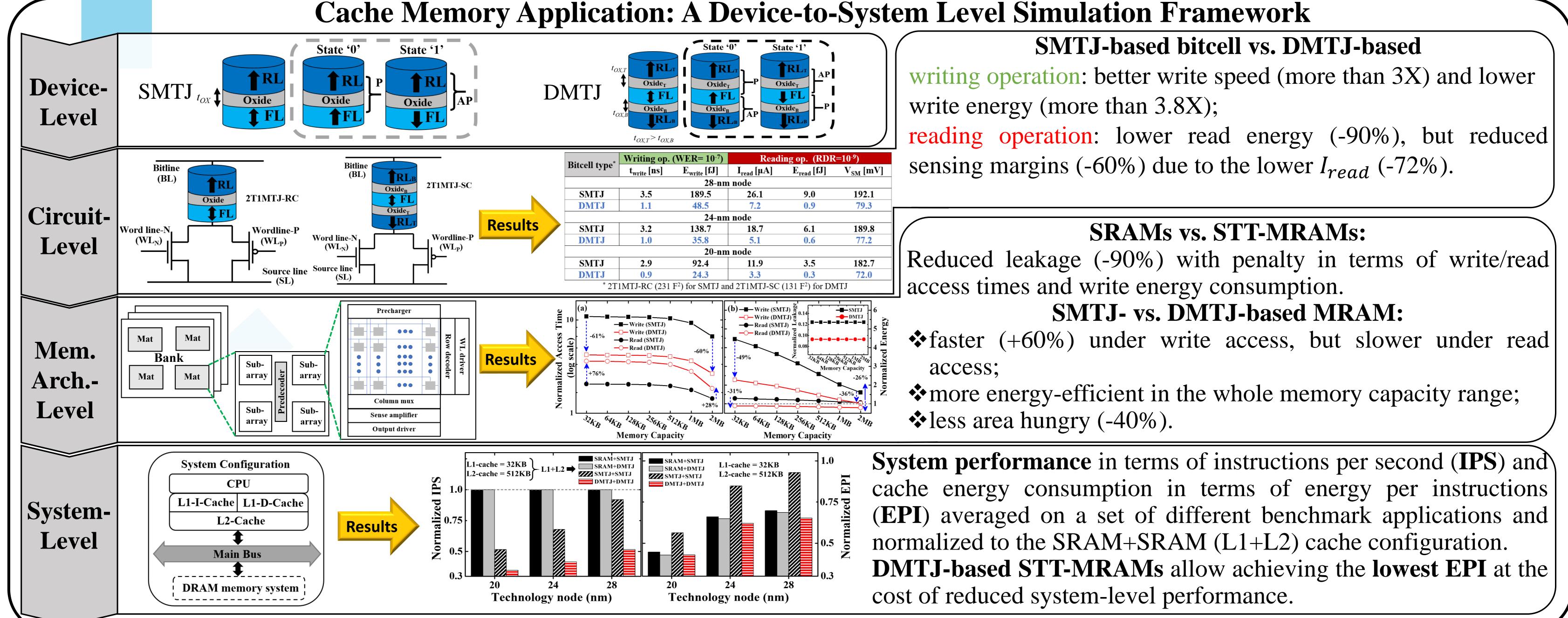

- Spin-transfer torque magnetic RAMs (STT-MRAMs) have recently gained keen interest for non-volatile cache memory applications thanks to their potential for low-power and high-speed operation, compatibility with CMOS process, and high integration density.

- The technology-scalability of STT-MRAMs still remains challenging, mainly due to the need to reduce the switching currents required for information writing.

- The aforementioned challenge can be addressed by using double-barrier magnetic tunnel junctions (DMTJs) with two reference layers (RLs) instead of conventional single-barrier MTJs (SMTJs).

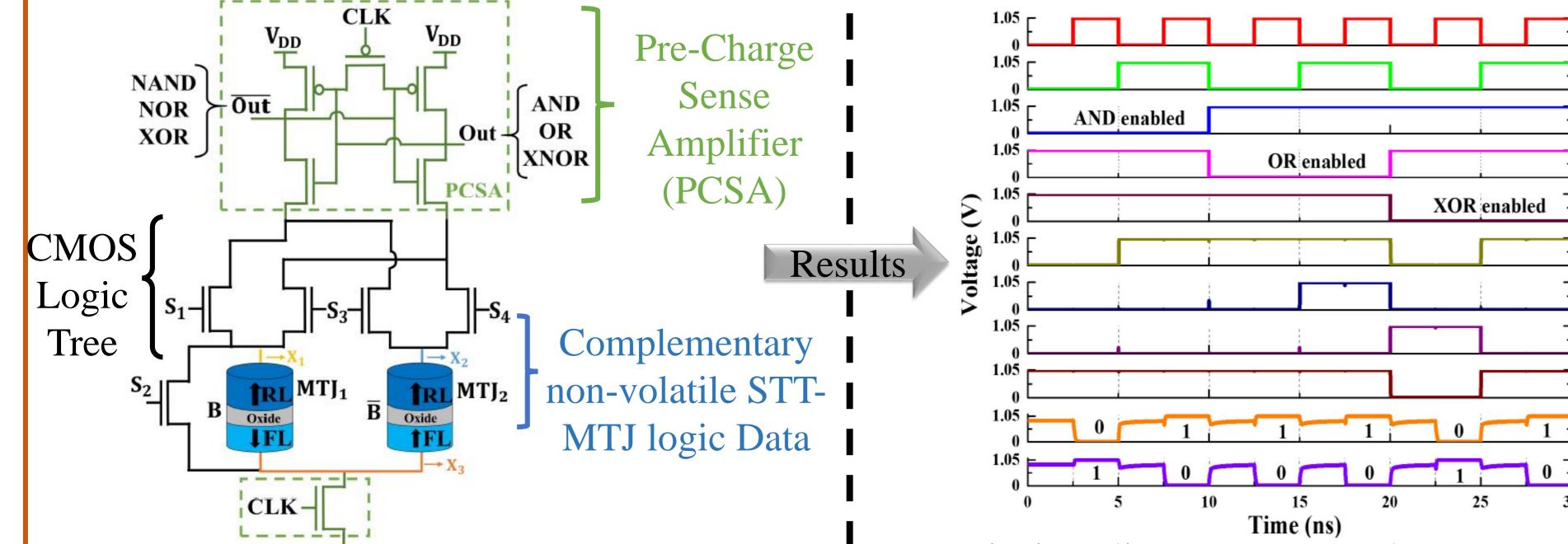

- Additionally, STT-MTJ based circuits have shown attractive potential to design efficient non-volatile logic-in-memory (NV-LIM) architectures, which assure low power and increased speed.

# **Logic-In-Memory Application: Reconfigurable CMOS/STT-MTJ Non-Volatile Circuit**

POST-LAYOUT SIMULATION RESULTS FOR THE PROPOSED AND THE STATE-OF-THE-ART HYBRID CMOS/STT-MTJ NV LOGIC CIRCUITS

| Design                          | Operation  | Delay (ps) | Energy (fJ) |

|---------------------------------|------------|------------|-------------|

| Proposed circuit                | AND/OR/XOR | 136.6      | 8.0         |

| State-of-the-art circuit (2014) | AND        | 128.3      | 4.8         |

| State-of-the-art circuit (2018) |            | 113.2      | 3.9         |

| State-of-the-art circuit (2014) | XOR        | 127.0      | 6.2         |

| State-of-the-art circuit (2018) |            | 94.5       | 4.5         |

| State-of-the-art circuit (2014) | OR         | 95.2       | 5.6         |

| State-of-the-art circuit (2018) |            | 91.8       | 4.6         |

The design leads to increase both delay (+29% on average) and energy (+66% on average) due to the larger number of transistors. However, a reconfigurability is offered by the proposed circuit, allowing multiple logic operations by the same architecture.

#### Proposed hybrid CMOS/STT-MTJ circuit.

Timing diagram. Note: the non-volatile logic input is B = 1

### Conclusions

#### **Cache memory applications**

- The use of DMTJs instead of conventional SMTJs in STT-MRAMs cache applications has been investigated through a device-to-system level simulation framework.

- Obtained results prove that DMTJ-based STT-MRAMs are credible candidates for replacing conventional semiconductor-based cache memories for the nextgeneration of low-power microprocessors with on-chip non-volatility.

#### Logic in memory applications

Input A

AND\_i

OR\_in signal

Out

- A new hybrid CMOS/STT-MTJ NV logic design is proposed, which allows implementing multiple logic functions (i.e. AND/OR/XOR) within a single circuit architecture.

- Obtained results show that, when compared to state-of-the-art designs, our circuit exhibits a penalty in both delay and energy due to the use of a larger number of transistors. Nevertheless, the operation flexibility offered by the proposed circuit represents a promising feature to reduce area occupancy and design complexity in NV-LIM circuit applications.

**E**nICS

**Emerging Nanoscaled** Integrated Circuits and Systems Labs

Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemistica

#### These works were(will be) presented in:

1. E. Garzón, et. al., "Device-to-System Level Simulation Framework for STT-DMTJ Based Cache Memory," IEEE International Conference on Electronics Circuits and Systems (ICECS), Genova, Nov. 29, 2019. 2. E. Garzón, et. al., "Reconfigurable CMOS/STT-MTJ Non-Volatile Circuit for Logic-in-Memory Applications," Accepted and to be presented in: IEEE Latin American Symposium on Circuits and Systems (LASCAS), San José, Costa Rica, 2020.

Advanced Circuits Research Center