# **2020 Research Day** Neural Network Analog-to-Digital & Digital-to-Analog Converters using Floating-Gate Memristors Loai Danial and Shahar Kvatinsky

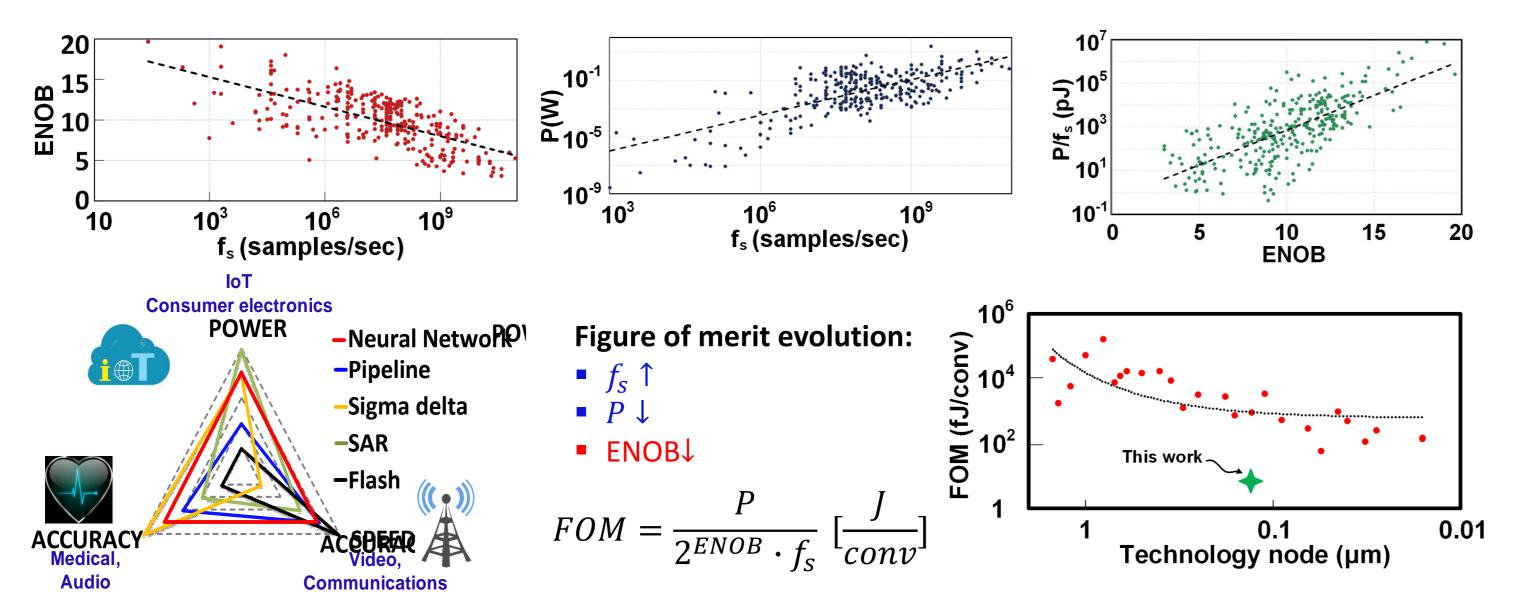

CMOS DATA CONVERTERS ARE SPECIAL PURPOSE APPLICATIONS DUE TO THE SPEED-POWER-ACCURACY TRADEOFF

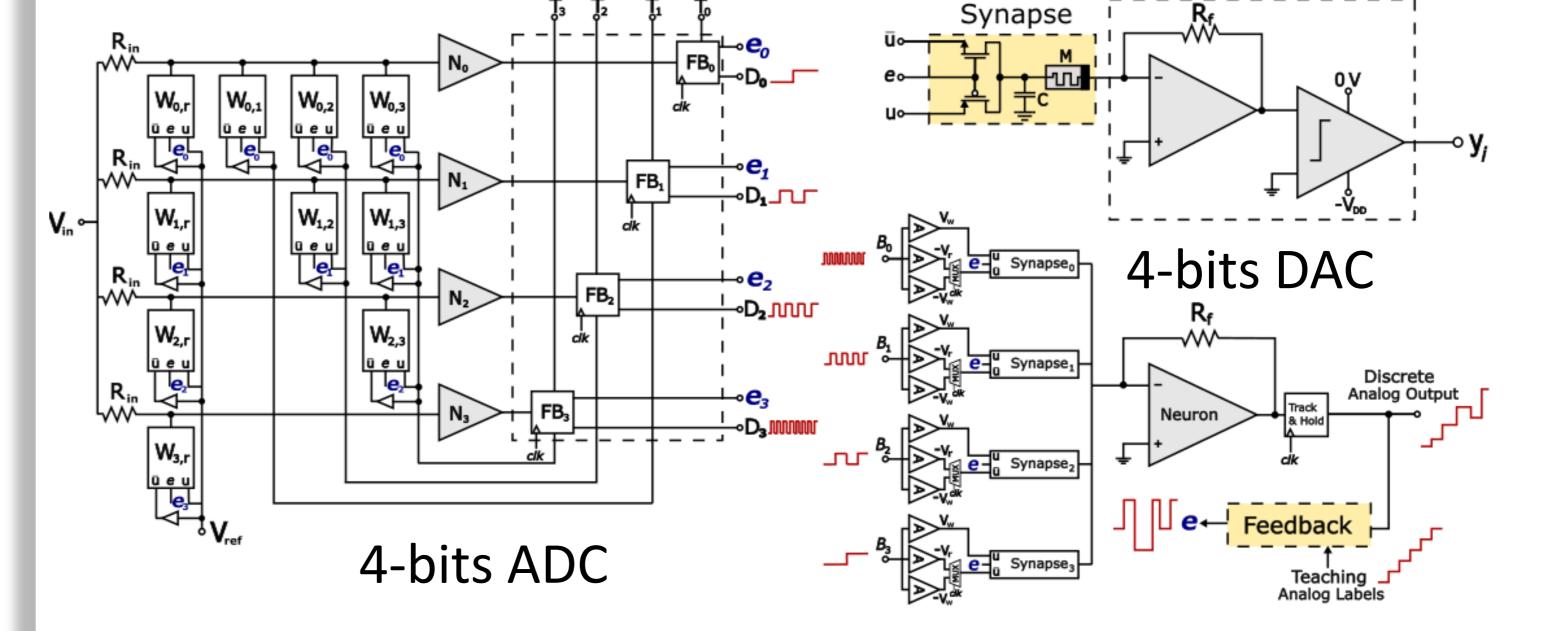

### NEURAL NETWORK ADC<sup>[2]</sup> & DAC<sup>[3]</sup>

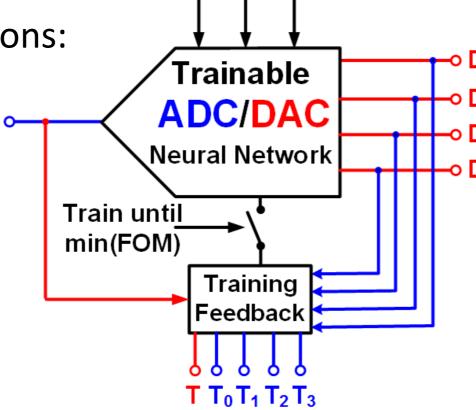

#### SOLUTION: REAL-TIME TRAINABLE DATA CONVERTERS USING MEMRISTORS<sup>[1]</sup>

Trainable data converters using supervised learning algorithms

• Data converter architecture for general purpose applications:

-Full-scale voltages V<sub>FS</sub>

-Number of bits N

-Sampling frequencies f<sub>s</sub>

- -Sampling nequencies  $J_s$

- -Logarithmic quantization

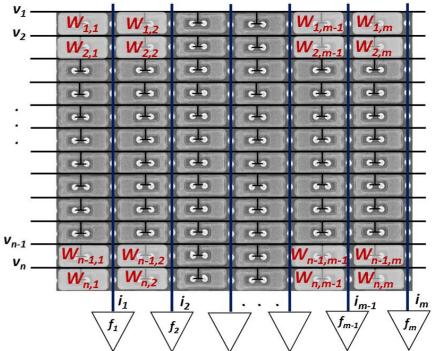

- Implemented as artificial neural network architectures

- Multi-level memristive devices used as artificial synapses

$f_s N V_{FS}$

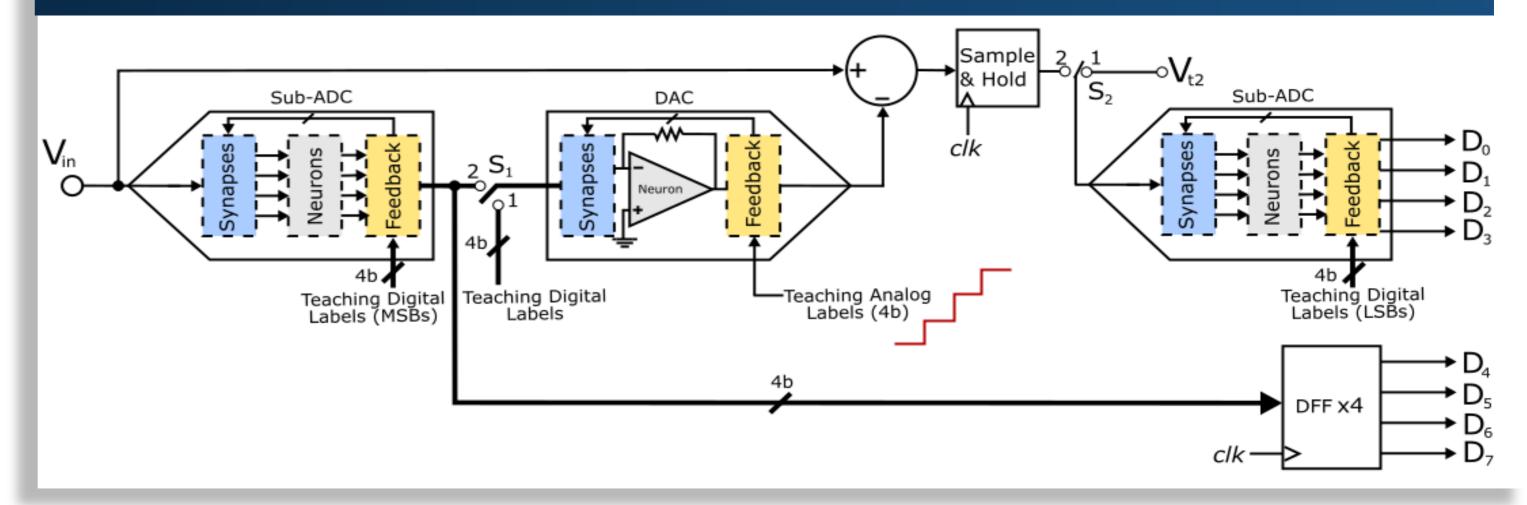

#### PIPELINED NEURAL NETWORK ADC FOR HIGH-RESOLUTION <sup>[4]</sup>

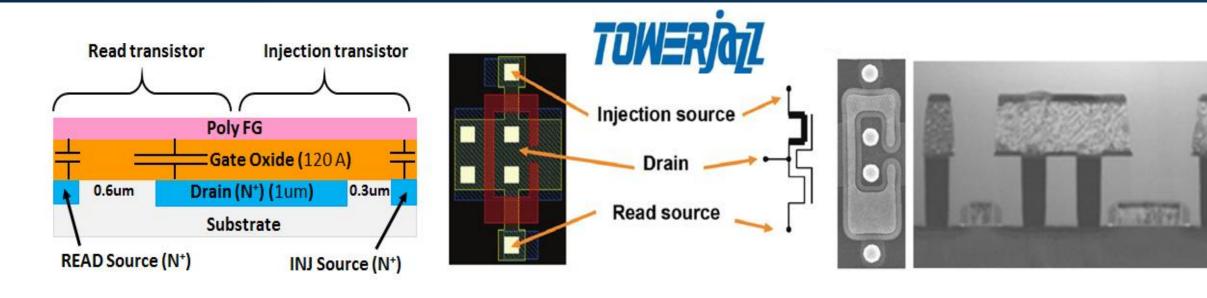

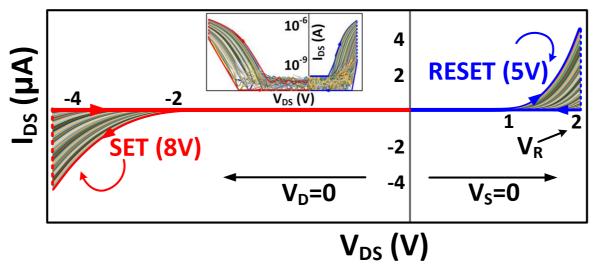

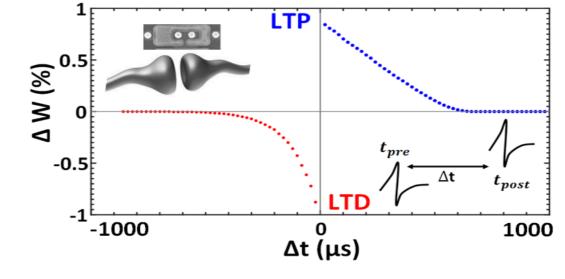

### METHODS: A TWO-TERMINAL FLOATING-GATE MEMRISTIVE DEVICE FOR ANALOGUE NEUROMORPHIC COMPUTING<sup>[5-6]</sup>

1. Experimental demonstration of trainable multiply-accumulate using:

- i. A selector-free integrated array of two-terminal floating-gate memristive devices

- ii. Sub-threshold mode operation, and gradual tuning (65 resistive levels)

- iii. Standard 180nm CMOS process, ten-year data retention, and 100K endurance cycles

- i. Neuron activations and learning algorithms

- ii. Model for floating-gate memristive device

- iii. CAD framework: DRC, LVS, RC extraction

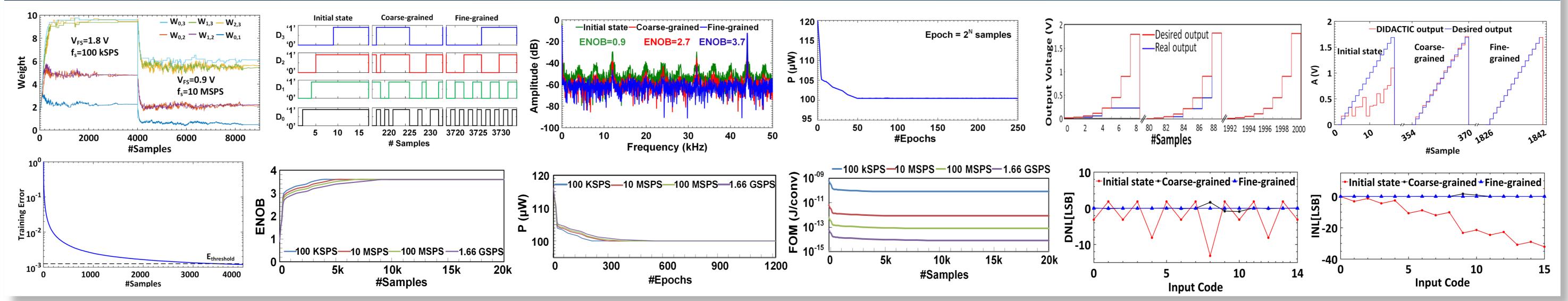

## PRELIMINARY RESULTS: BREAKING THROUGH THE SPEED-POWER-ACCURACY TRADEOFF

#### **CONCLUSIONS AND ONGOING WORK**

- ... We propose neural network data converters:

- i. Trained using machine learning algorithms

- ii. Demonstrated using floating-gate memristive devices in standard 180nm CMOS

\*This work is done in collaboration with TowerJazz

#### 2. These results show a potential to:

- i. break through the speed-power-accuracy tradeoff in conventional data converters

- ii. enable a generic architecture for general purpose applications

3. Ongoing work investigates fabrication of large-scale data conversion architectures using deep neural networks and mixed-signal circuits [4][7-8]

#### PUBLICATIONS AND ACKNOWLEDGEMENTS

[1] L. Danial, & S. Kvatinsky, "Real-Time Trainable Data Converters for General Purpose Applications," NANOARCH, 2018.

[2] L. Danial et al., "Breaking Through the Speed-Power-Accuracy Tradeoff in ADCs Using a Memristive Neuromorphic Architecture," TETCI, 2018.

[3] L. Danial et al., "DIDACTIC: A Data-Intelligent Digital-to-Analog Converter with a Trainable Integrated Circuit Using Memristors," JETCAS, 2018.

[4] L. Danial et al., "A Pipelined Memristive Neural Network Analog-to-Digital Converter," ISCAS, 2020.

[5] L. Danial et al., "A Low-Power Memristive Operation Mode of Two-Terminal Floating-Gate Transistors for Analogue Neuromorphic Computing," Nature Elect., 2019.

[6] L. Danial et al., "Modeling a Floating-Gate Memristive Device for Computer-Aided Design of Neuromorphic Computing," DATE, 2020.

[7] L. Danial et al., "Delta-sigma modulation neurons for high-precision training of memristive synapses in deep neural networks," ISCAS, 2019.

[8] L. Danial et al., "Logarithmic Neural Network Data Converters Using Memristors for Biomedical Applications," BioCAS, 2019.

rt., 2019. Advanced Circuits Research Center