# 2020 Research Day

## **1T-FeFET Memory Architecture**

Mor Dahan, Advisor: Prof. Shahar Kvatinsky Asic<sup>2</sup> Group

Motivation

The growing demand for fast, low power and non-volatile memories makes the FeFET promising technology. It is a high-K transistor with high-density integration, low-power scalability and CMOS-compatible.

#### **Ferroelectric Transistor**

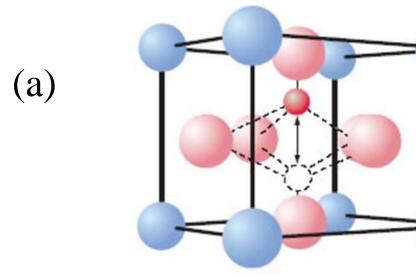

Ferroelectric materials are dielectric crystals which show

spontaneous electric polarization

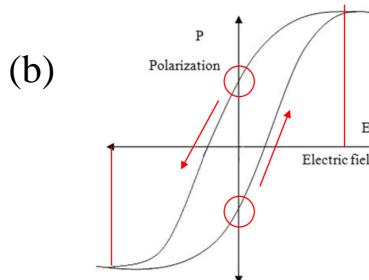

Ferroelectric materials. (a) Ferroelectric crystal structure. (b) P-E hysteresis curve of ferroelectric crystal. Integrating ferroelectric layer in the gate stack of MOSFET enables storing digital data in terms of polarization direction.

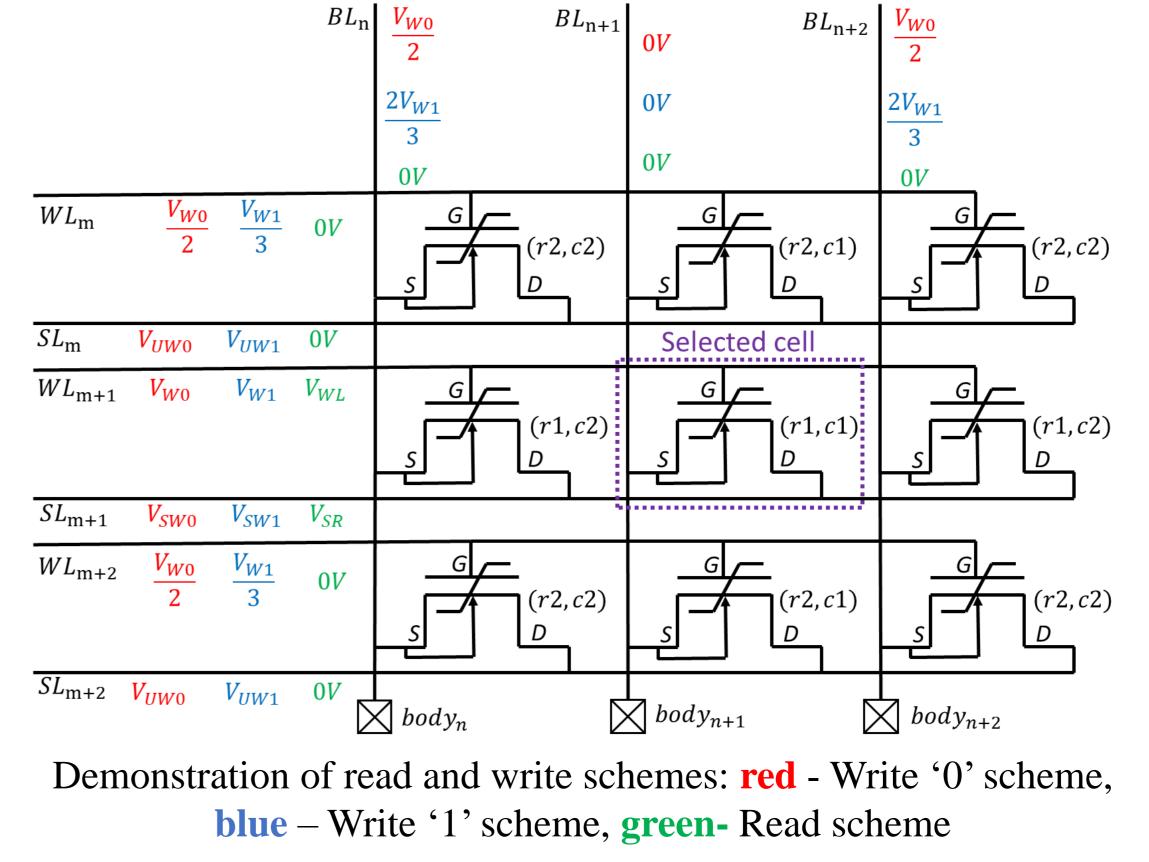

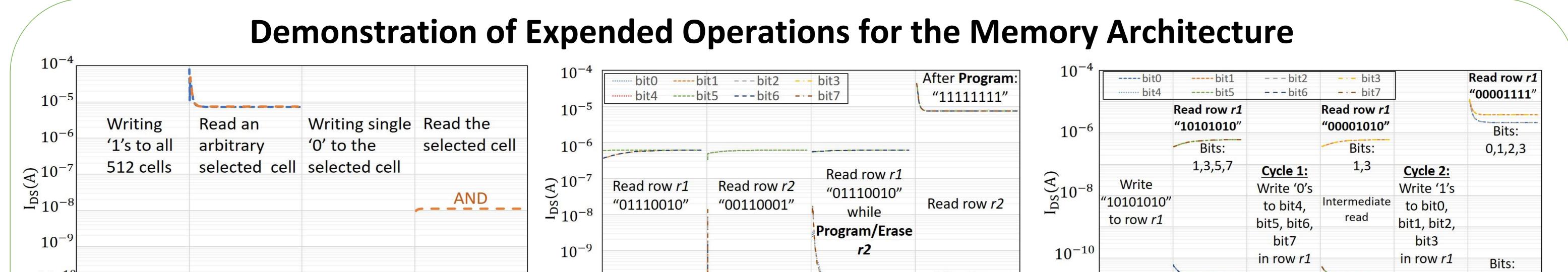

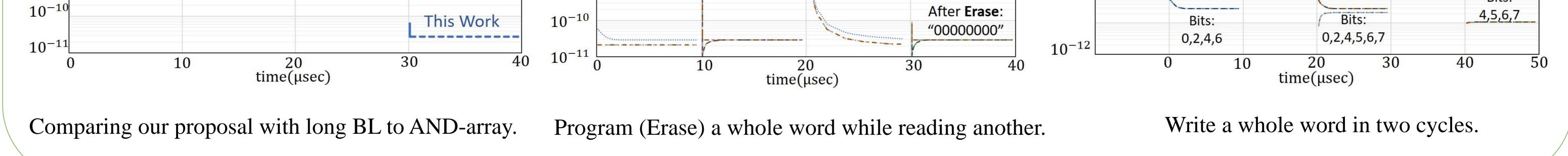

### 1T-FeFET Memory Architecture for Disturb Reduction using Mixed Writing Scheme

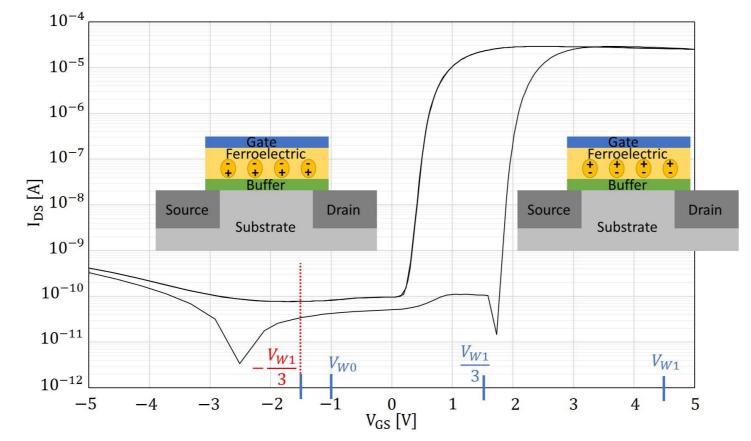

IDS-VGS curves of a FeFET, the transistor structure, and the corresponding polarization direction. Red - write error demonstration for hysteresis with asymmetric switching voltages.

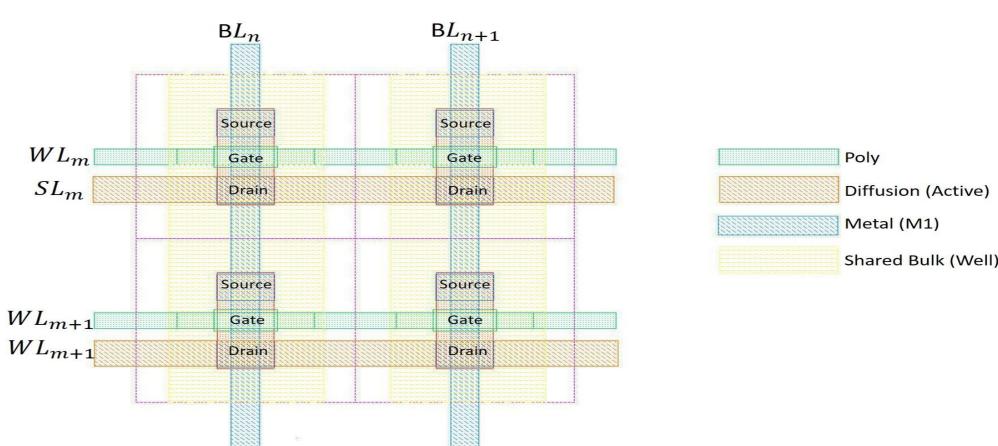

Schematic layout of our proposed structure with vertical poly and diffusion and horizontal metal and shared bulk.

This is non-volatile memory (NVM) with single element per cell and non-destructive readout operation.

#### **Future Work**

In-memory computing using the unique properties of the FeFET and the 1T-FeFET architecture.

- Utilize FeFET's accumulative switching for analog

applications.