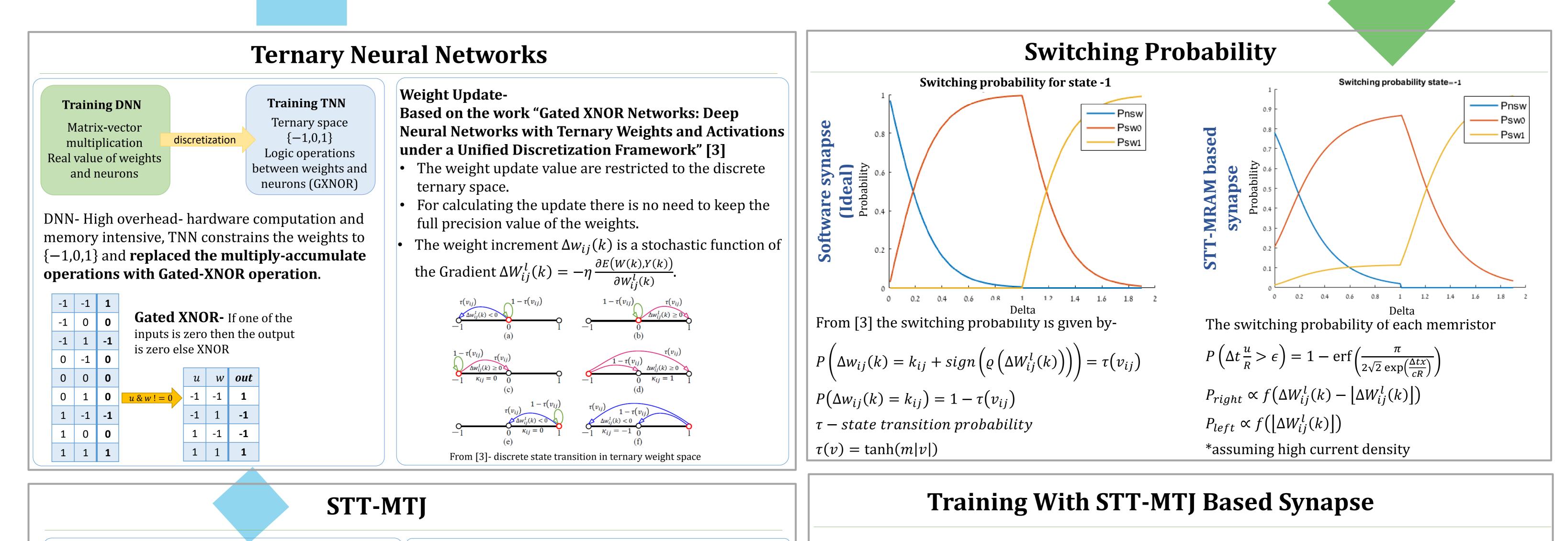

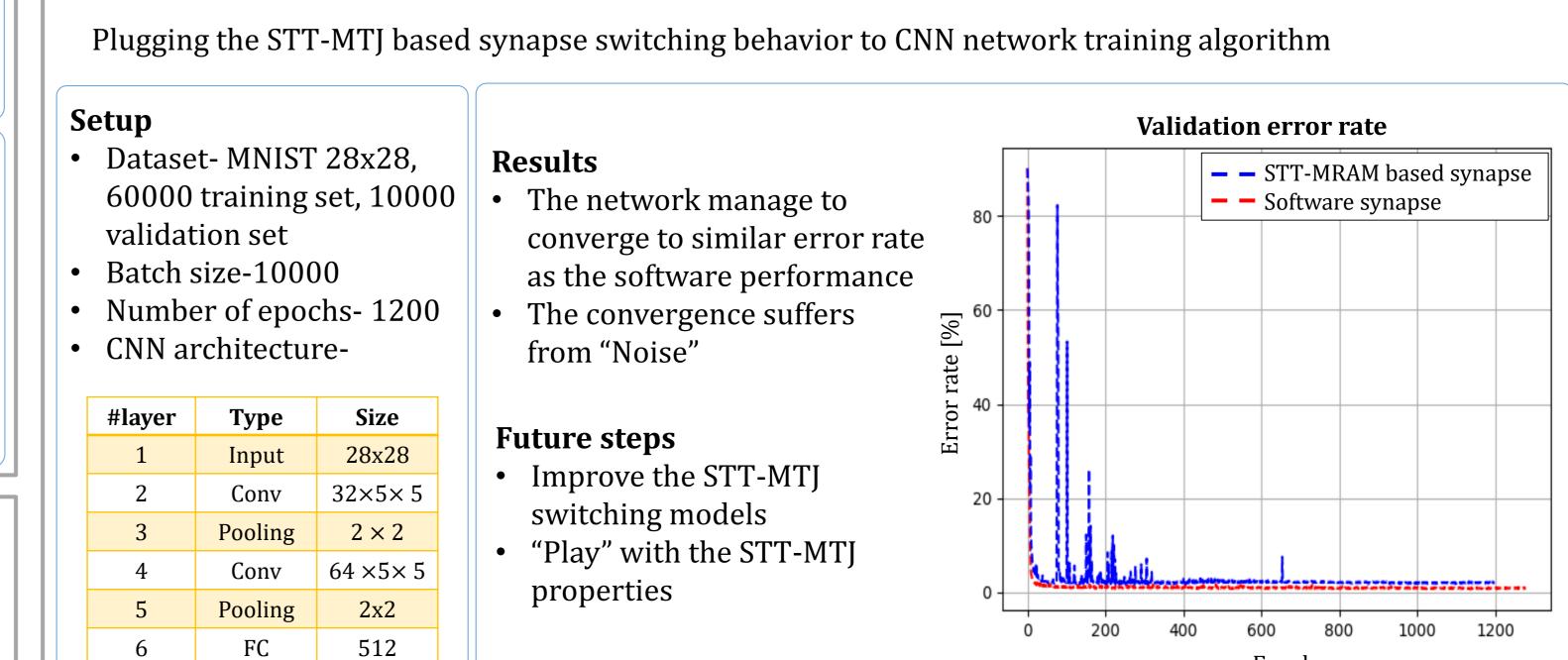

# **2020 Research Day** MTJ-Based Hardware Synapse Design for Ternary Deep Neural Networks Tzofnat Greenberg, Ben Perach, Daniel Soudry, and Shahar Kvatinsky

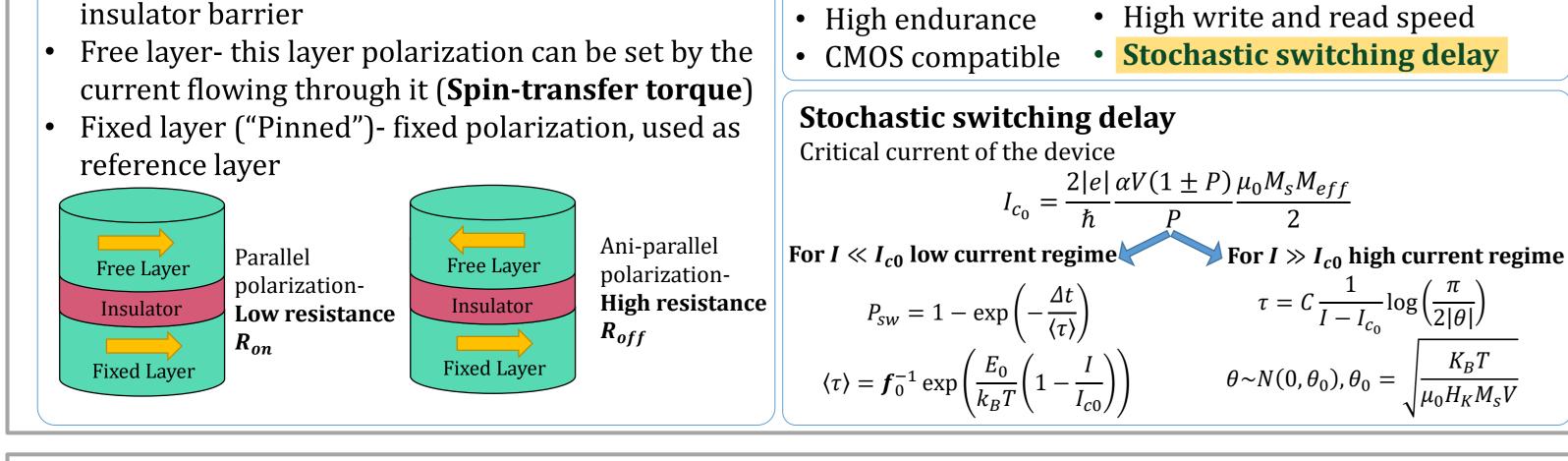

#### Magnetic tunnel junction (MTJ)

• Two ferromagnetic electrodes separated by an

#### **Properties** • Nonvolatile

• Low power consumption

M<sub>R</sub>

R<sub>off</sub>

Ron

R<sub>off</sub> R<sub>off</sub>

R<sub>off</sub>

R<sub>on</sub>

R<sub>on</sub>

Notice-  $|x| \in \{0,1\}$

State

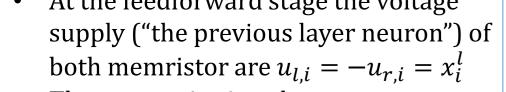

# **Ternary Synapse Based STT-MTJ**

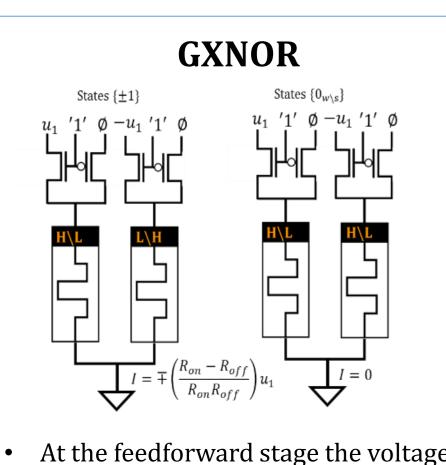

**Need to support 3 operations:**

1. GXNOR ("read") 2. Inverse read

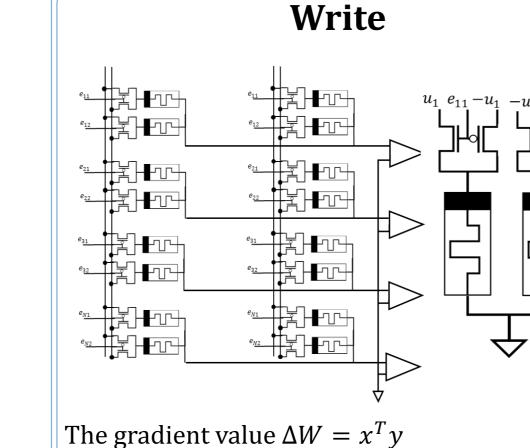

3. Write

## **Inverse** read $\sum_{i=1}^{n} (W_{1i}^{l} - W_{1i}^{r}) y_{i} = \sum_{i=1}^{n} W_{1i} y_{i}$

$\sum_{W_{1i}^l y_i}^n w_{1i}$

$\sum_{i=1}^{n} W_{1i}^{r} y_{i}$

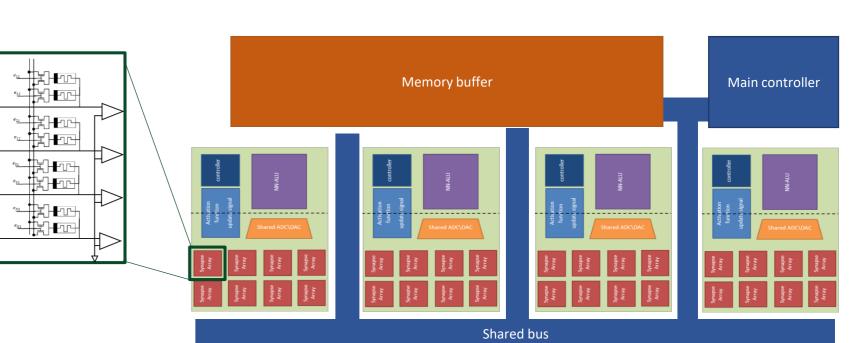

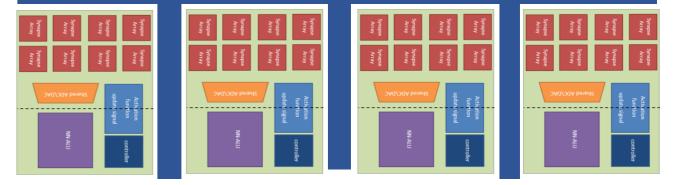

## **TNN Hardware Architecture**

∰g]∎or

╇ ╪ ╋

┉╇<sub>╋</sub> ┉╇<sub>╋</sub>

## Improve power consumption and

10

run-time

**Initial results**

• Reduce memory accesses

FC

• In-memory computation of the GXNOR (= dot-product)

### Main architecture concept

- Tile based architecture

- Each tile contain: several synapse arrays,

• The current is given by  $\left(\frac{M_R - M_L}{M_L M_R}\right) u$

• Example u=-1

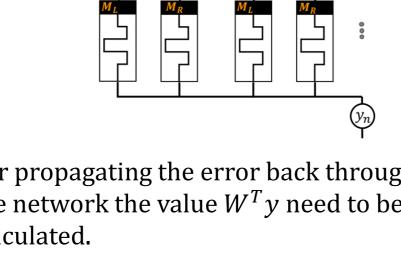

For propagating the error back through the network the value  $W^T y$  need to be calculated.

The rows acts as the input with voltage level *y*

The output current per column per memristor ( $H\L$ ) is summed and then compared.

```

\Delta W

e_{i1} = \begin{cases} sign([y_i]), & 0 < t < abs([y_1]) \end{cases}

abs([y_1]) < t < T_{wn}

The right memristor is updated with respect to

\Delta W - [\Delta W]

```

The left memristor is updated with respect to

$e_{i2}$  $(sign(y_i - |y_i|)), \quad 0 < t < abs(y_i - |y_i|))$  $abs(y_i - \lfloor y_i \rfloor) < t < T_{wr}$  shared local computation units (example: activation and its' derivatives), local buffer,

etc...

• Main controller to map each layer to one or more synapse arrays

#### **Reference**:

Epoch

1) Tzofnat Greenberg-Toledo, Ben Perach, Daniel Soudry, Shahar Kvatinsky "MTJ-Based Hardware Synapse Design for Quantized Deep Neural Networks". CoRR abs/1912.12636 (2019)

2) Vincent, Adrien F., et al. "Spin-transfer torque magnetic memory as a stochastic memristive synapse for neuromorphic systems." IEEE transactions on biomedical circuits and systems 9.2 (2015): 166-174

- 3) Vincent, Adrien F., et al. "Analytical macrospin modeling of the stochastic switching time of spin-transfer torque devices." IEEE Transactions on Electron Devices 62.1 (2015): 164-170.

- 4) Deng, Lei, et al. "Gated XNOR Networks: Deep Neural Networks with Ternary Weights and Activations under a Unified Discretization Framework." arXiv preprint arXiv:1705.09283 (2017).