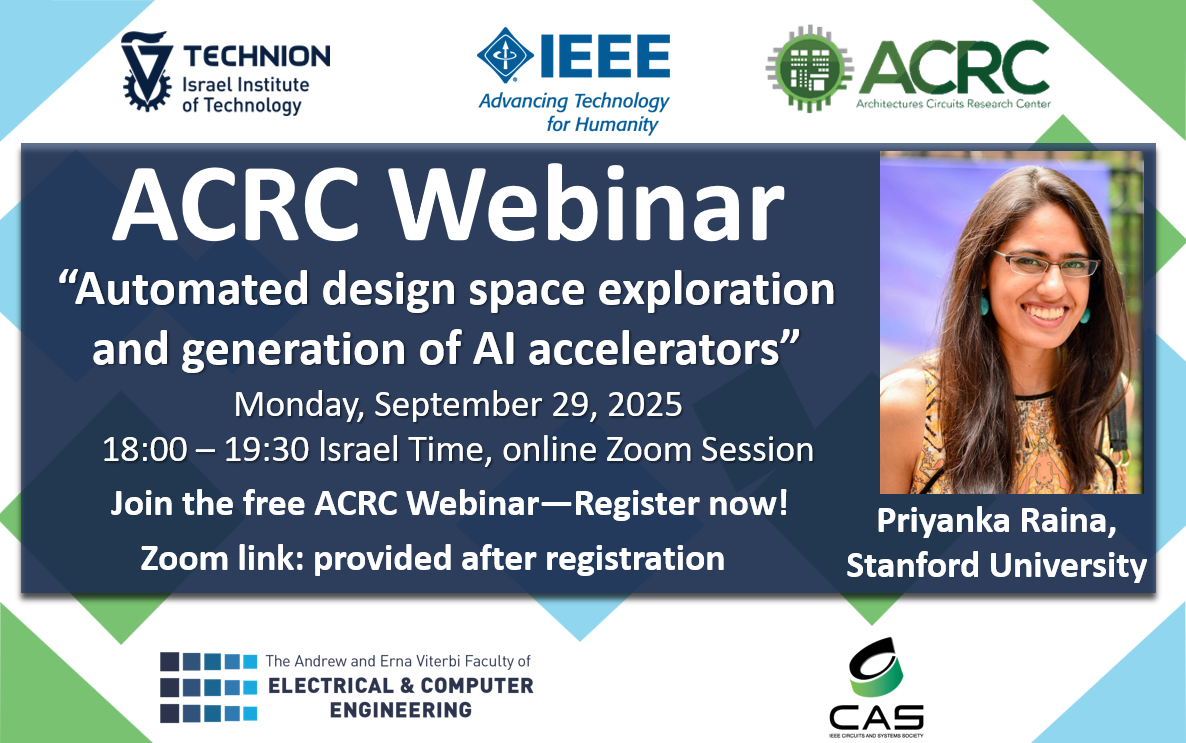

Date: September 29, 2025 – Monday

Time: 18:00 – 19:30 Israel Time

Speaker: Prof. Priyanka Raina, Stanford University

Language: English

Register Here

Abstract:

Designing high performance and energy efficient AI accelerators requires significant engineering effort, and as the rapidly evolving field of machine learning develops new models, the current approach of designing ad hoc accelerators does not scale. In this talk, I will present our ongoing research on a high-level synthesis (HLS)-based framework for design space exploration and generation of hardware accelerators for AI. Given architectural parameters, such as datatype, scaling granularity, compute parallelism and memory sizes, the framework generates a performant fabrication-ready accelerator. Accelerators generated through this framework have been taped out in several chips, targeting various workloads including convolutional neural networks and transformer networks. In this talk, I will present the generator framework, and show how we can also use it as a benchmarking tool for designs leveraging emerging technologies.

Biography:

Priyanka Raina received the B.Tech. degree in Electrical Engineering from IIT Delhi in 2011, and the M.S. and Ph.D. degrees in Electrical Engineering and Computer Science from MIT in 2013 and 2018, respectively. She was a Visiting Research Scientist with NVIDIA Corporation in 2018. Since 2018 she is an Assistant Professor of Electrical Engineering at Stanford University, where she works on domain-specific hardware architectures and agile hardware–software codesign methodology. Dr. Raina is a 2018 Terman Faculty Fellow. She was a co-recipient of the Best Demo Paper Award at VLSI 2022, the Best Student Paper Award at VLSI 2021, the IEEE Journal of Solid-State Circuits (JSSC) Best Paper Award in 2020, the Best Paper Award at MICRO 2019, and the Best Young Scientist Paper Award at ESSCIRC 2016. She has won the DARPA Young Faculty Award in 2024, Sloan Research Fellowship in 2024, the National Science Foundation (NSF) CAREER Award in 2023, the Intel Rising Star Faculty Award in 2021, and the Hellman Faculty Scholar Award in 2019. She was the Program Chair of the IEEE Hot Chips in 2020. She serves as an Associate Editor for the IEEE Journal of Solid-State Circuits and IEEE Solid-State Circuits Letters.

The webinar is free, but registration is required. Zoom link will be sent after registration.