Digital predistortion (DPD) has been widely adopted to keep RF power amplifier operating with high efficiency without losing linearity in the exiting 4G systems. It is expected that DPD will continue to be deployed in 5G systems. However, due to shifting from the single antenna to the multiple-input multiple-output (MIMO) phased array and continuously increased signal bandwidth, system designers face significant challenges in managing power consumption and meeting linearity requirement of wireless transmitters. In this talk, we will discuss how the recently developed machine learning techniques can be utilised to resolve some of the issues in linearizing 5G MIMO systems, including data-clustering assisted DPD for multiple dynamic configurations, model tree-based behavioural model construction and simplified model extraction techniques.

Anding Zhu received the Ph.D. degree in electronic engineering from University College Dublin (UCD), Dublin, Ireland, in 2004. He is currently a Professor with the School of Electrical and Electronic Engineering, UCD. His research interests include high-frequency nonlinear system modeling and device characterization techniques, high-efficiency power amplifier design, wireless transmitter architectures, digital signal processing, and nonlinear system identification algorithms. He has published more than 160 peer-reviewed journal and conference articles. Professor Zhu served as the Secretary of Administrative Committee (AdCom) of IEEE Microwave Theory and Techniques Society (MTT-S) in 2018. He is currently an Elected Member of MTT-S AdCom, the Chair of Electronic Information Committee and the Vice Chair of Publications Committee. He is also the Chair of MTT-S Microwave High-Power Techniques Committee and a Track Editor of IEEE Transactions on Microwave Theory and Techniques.

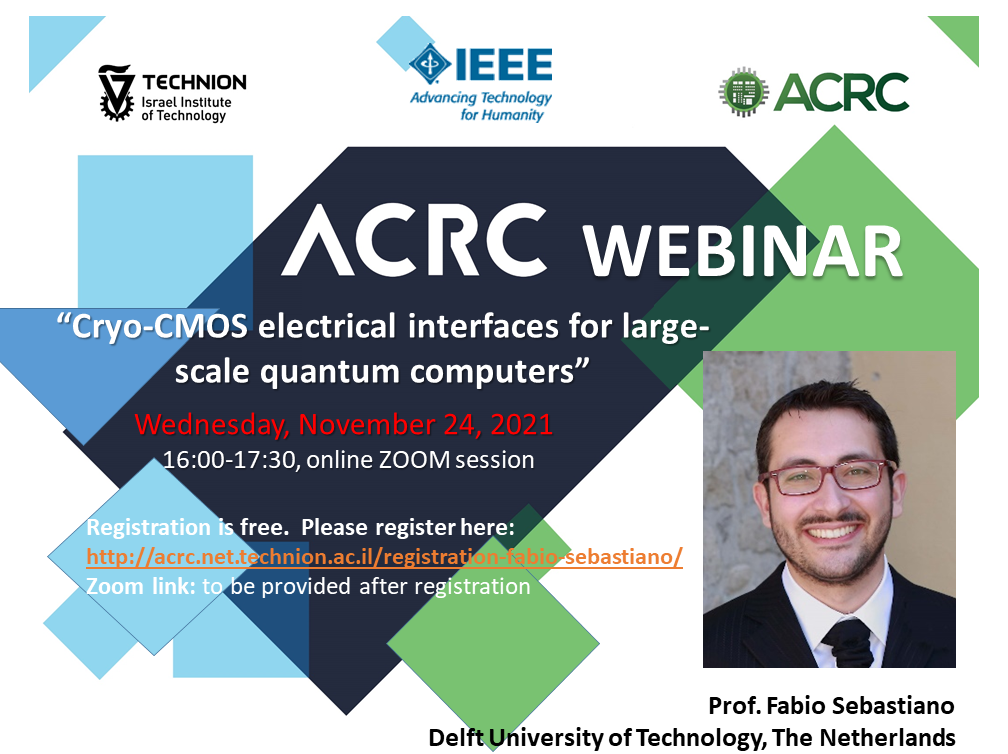

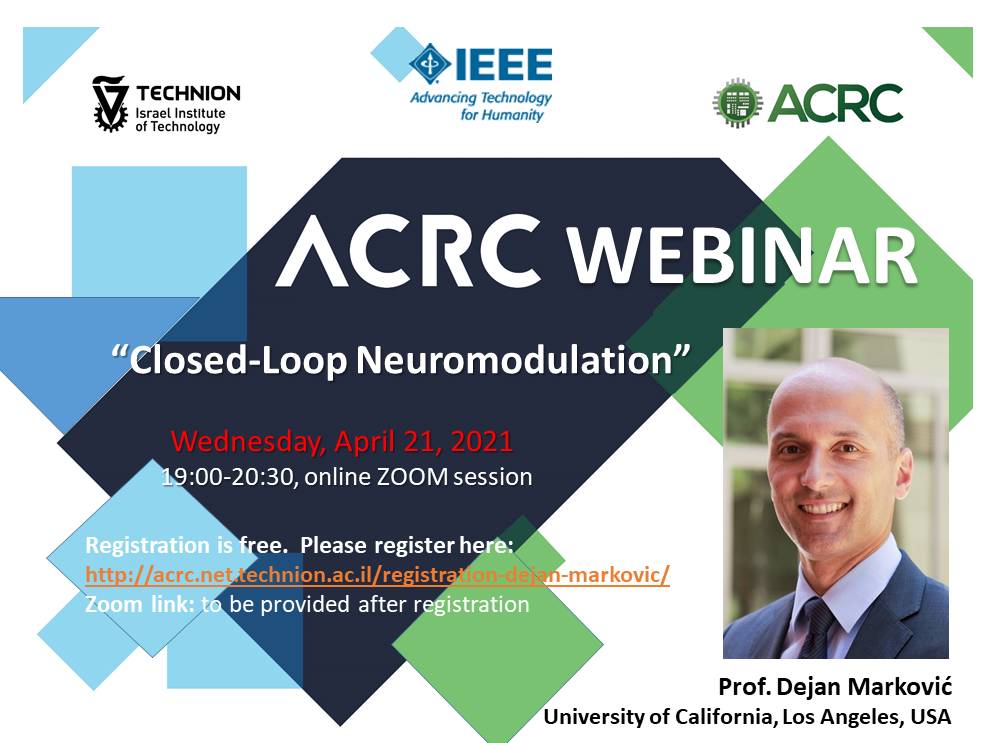

Important: The participation is free of charge, but registration is required

For more details and updates on the series of “ACRC Semiconductor Webinars” please follow our newsletters and our website